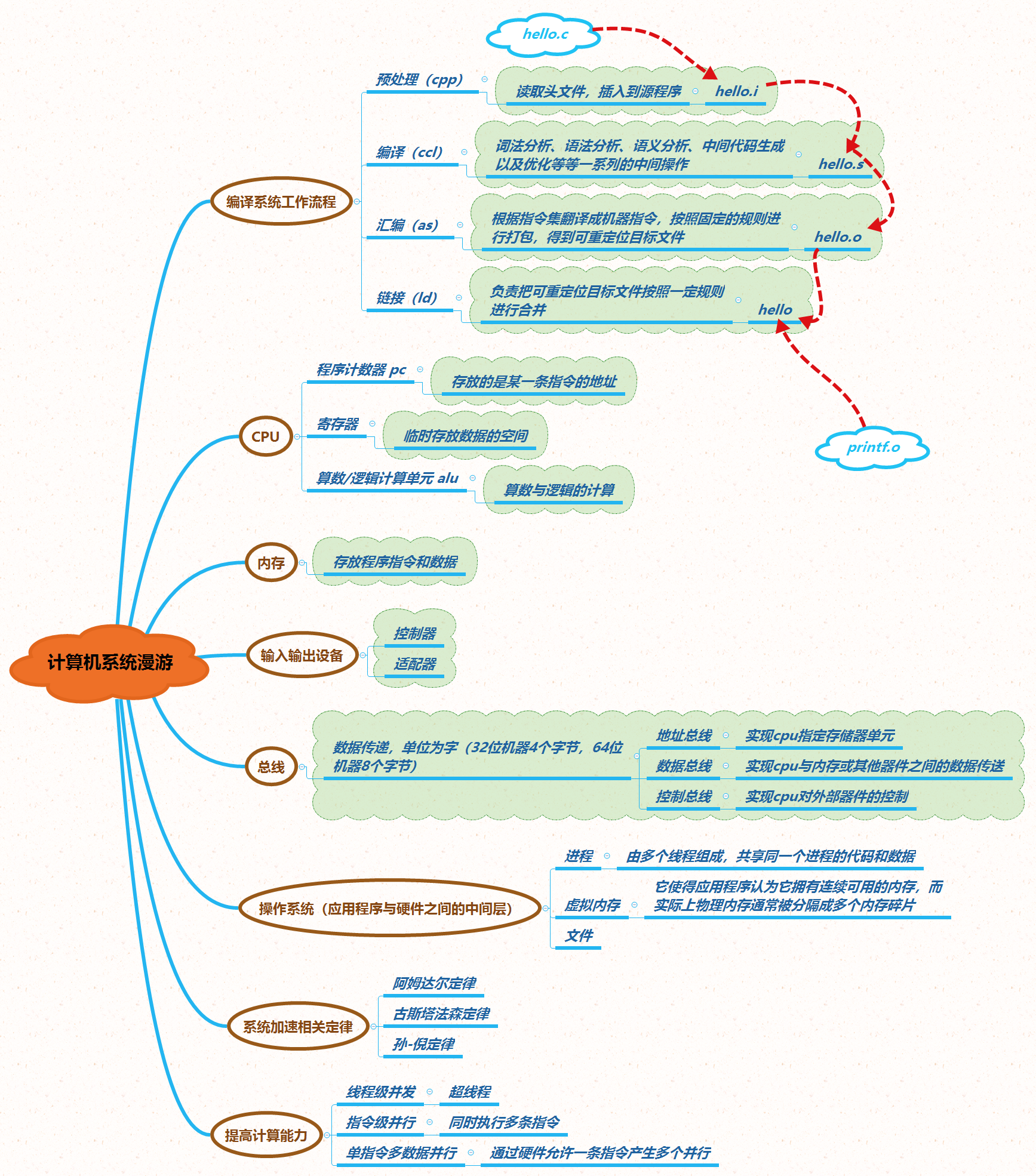

计算机系统漫游

总结大纲

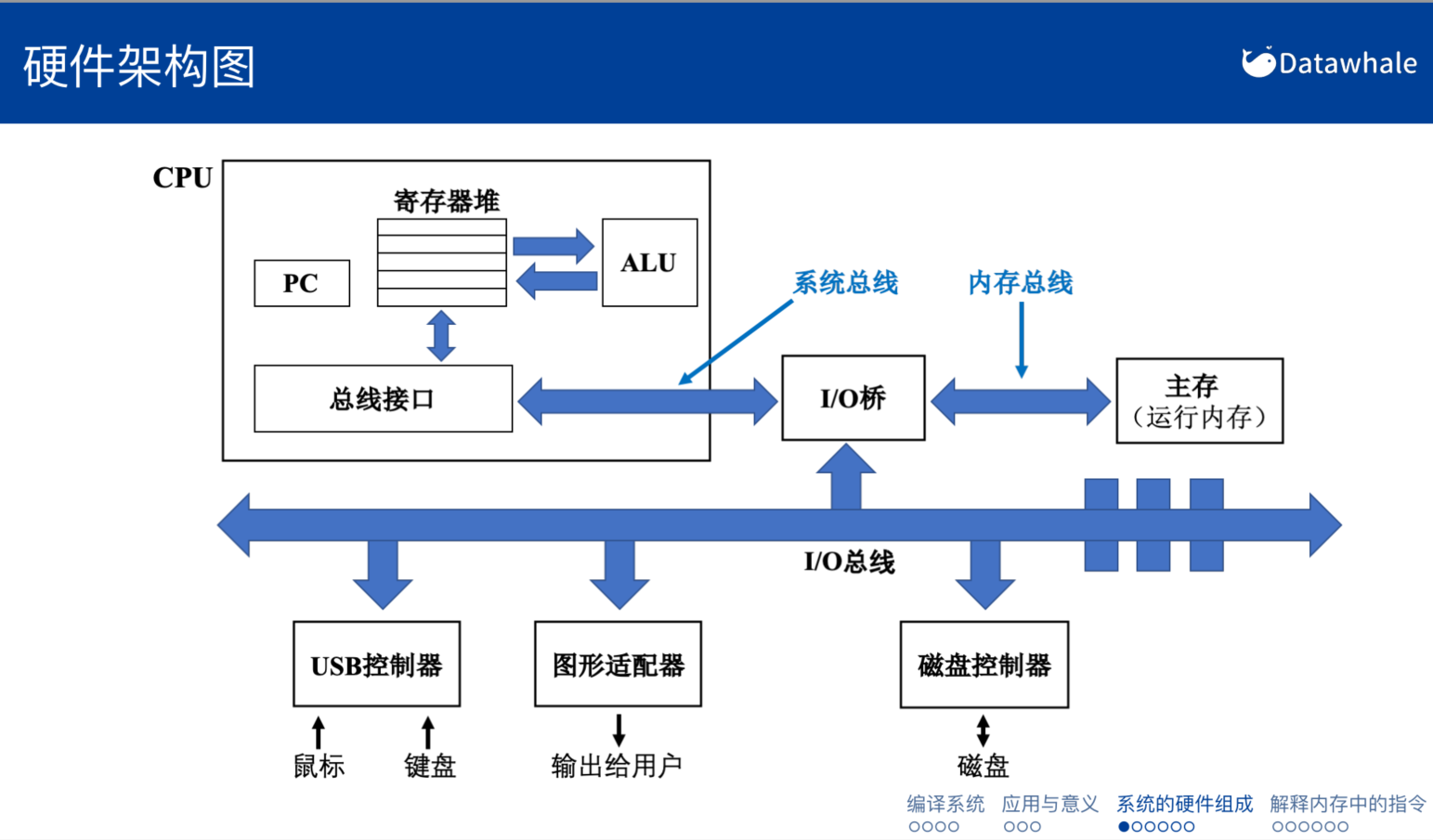

硬件架构图

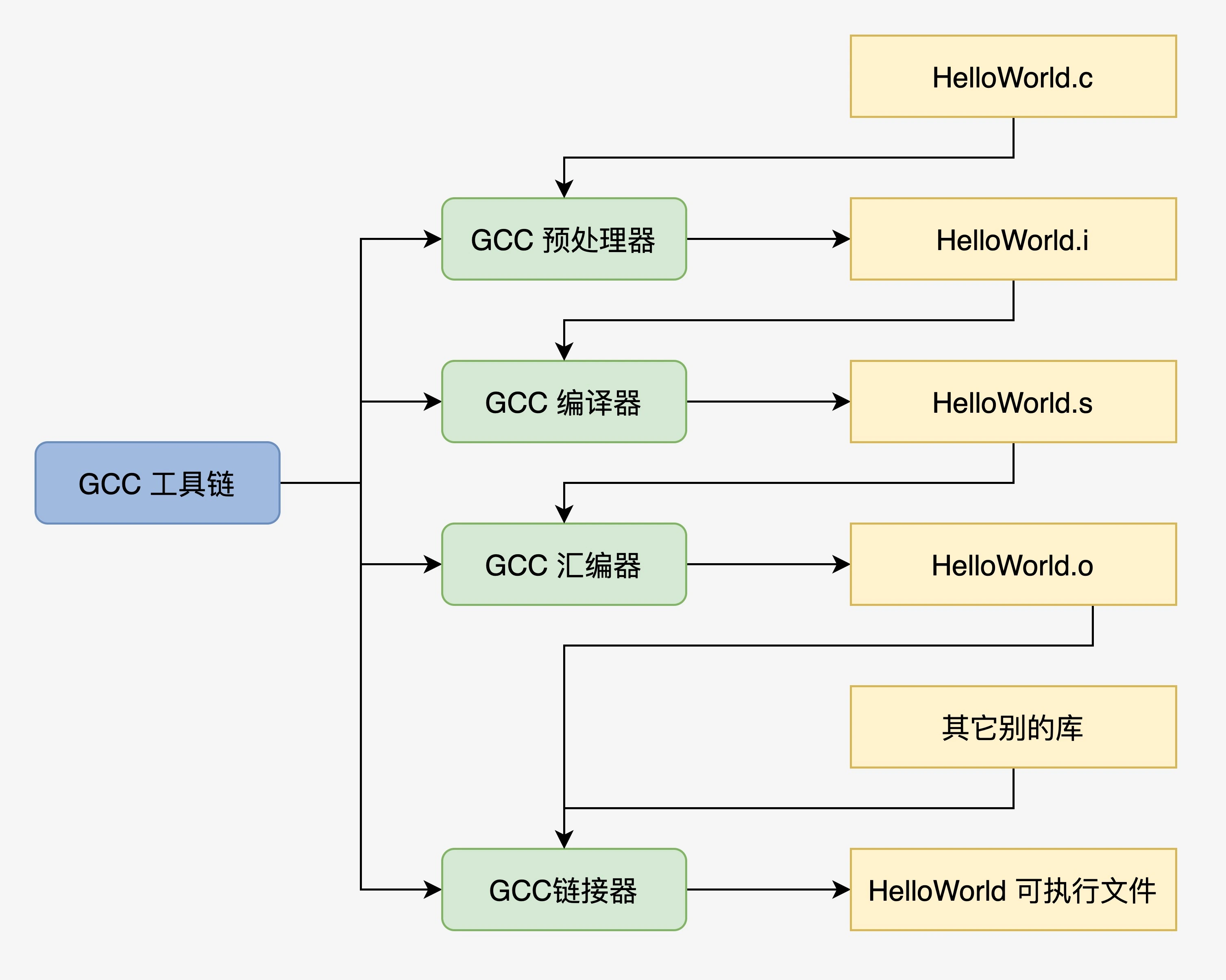

程序编译过程

- gcc HelloWorld.c -E -o HelloWorld.i 预处理:加入头文件,替换宏。

- gcc HelloWorld.c -S -c -o HelloWorld.s 编译:包含预处理,将 C 程序转换成汇编程序。

- gcc HelloWorld.c -c -o HelloWorld.o 汇编:包含预处理和编译,将汇编程序转换成可链接的二进制程序。

- gcc HelloWorld.c -o HelloWorld 链接:包含以上所有操作,将可链接的二进制程序和其它别的库链接在一起,形成可执行的程序文件。

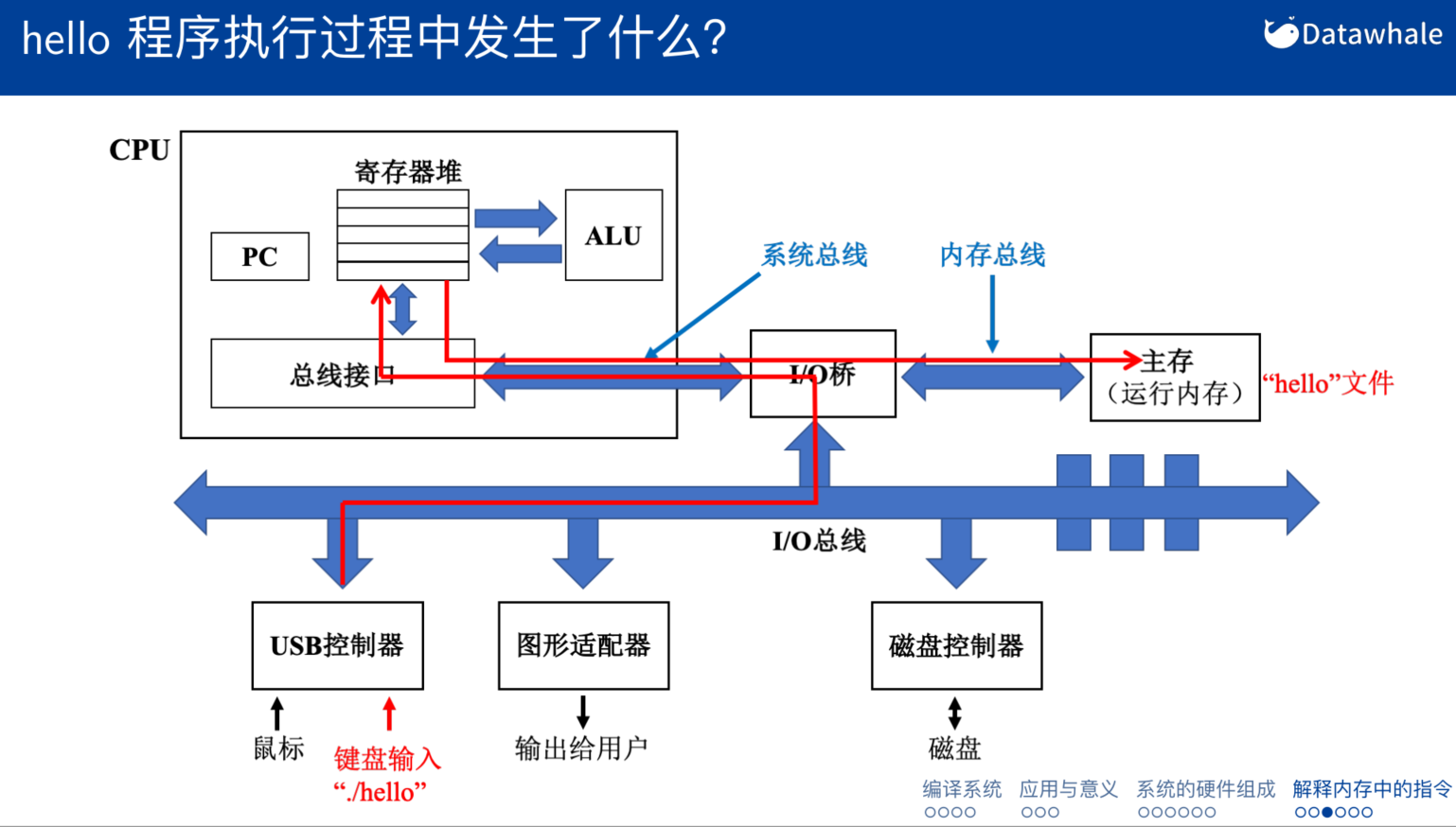

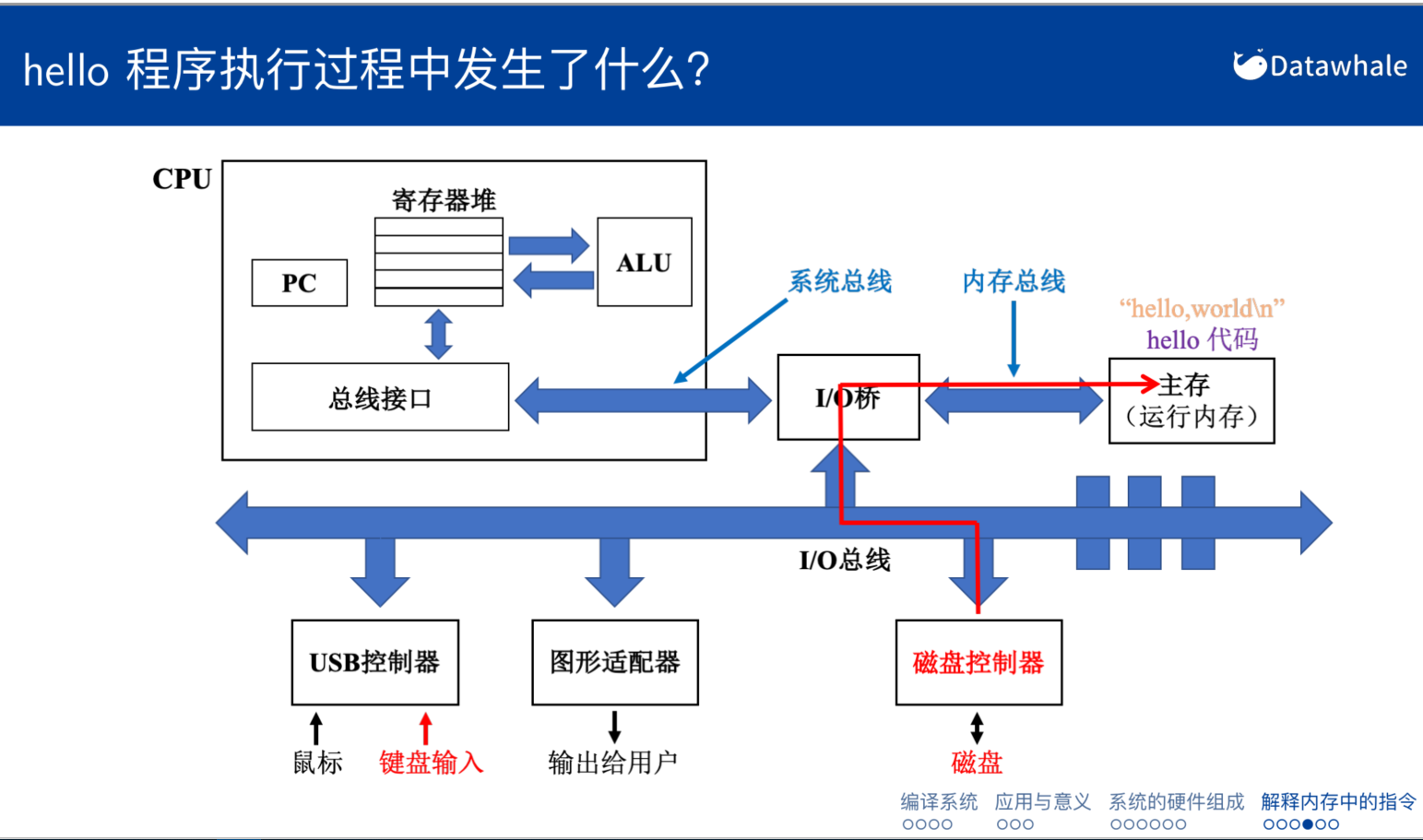

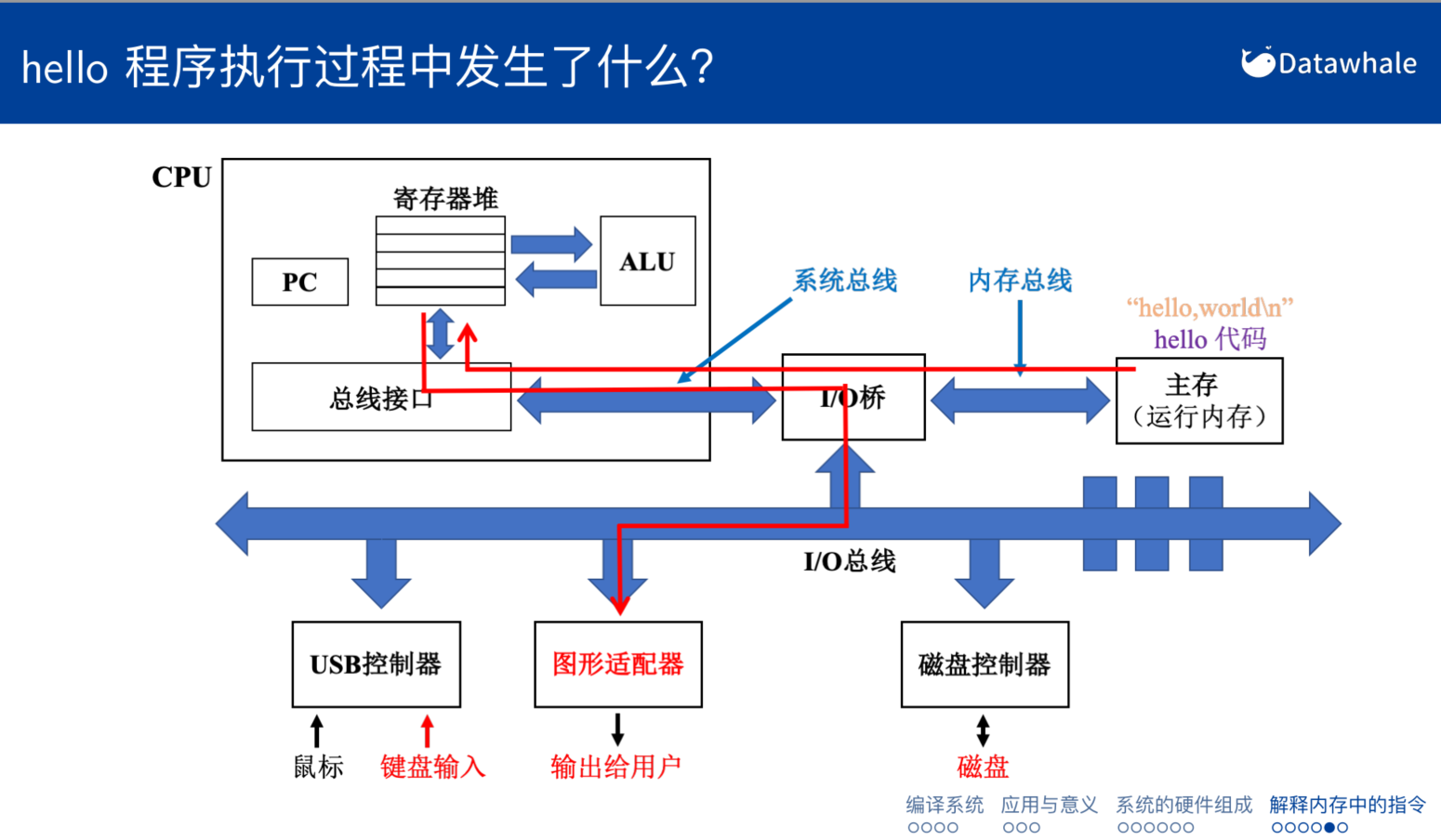

hello程序执行过程

- 首先我们通过键盘输入"./hello" 的字符串,shell 程序会将输入的字符逐一读入寄存器,处理器会把 hello 这个字符串放入内存中。

- 当我们完成输入,按下回车键时,shell 程序就知道我们已经完成了命令的输入, 然后执行一系列的指令来来加载可执行文件 hello。

- 这些指令将 hello 中的数据和代码从磁盘复制到内存。数据就是我们要显示输出的"hello , world\n" ,这个复制的过程将利用 DMA(Direct Memory Access)技术,数据可以不经过处理器,从磁盘直接到达内存。

- 当可执行文件 hello 中的代码和数据被加载到内存中,处理器就开始执行 main函数中的代码,main 函数非常简单,只有一个打印功能。

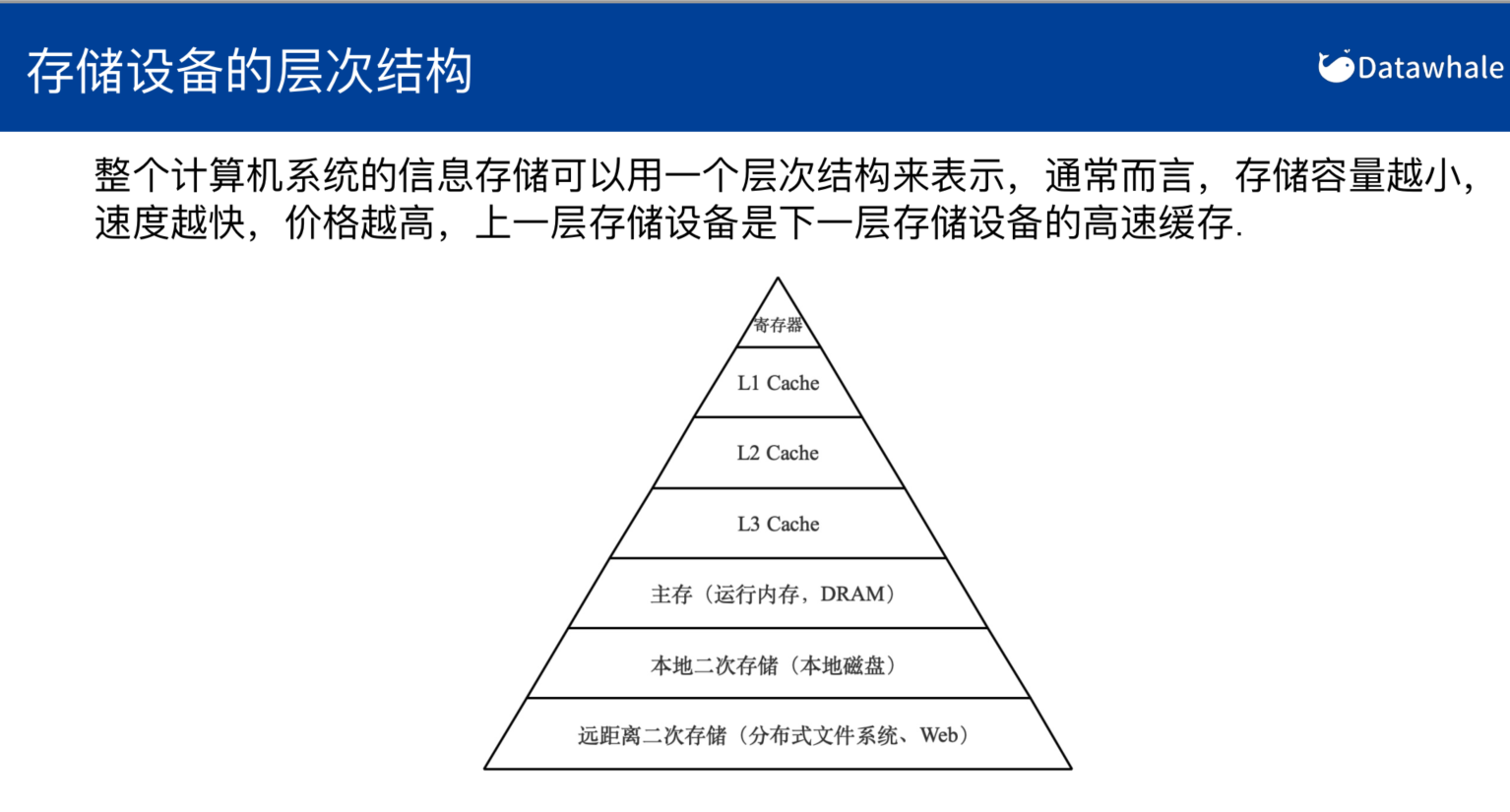

Cache

针对处理器和内存之间的差异,系统设计人员在寄存器文件和内存之间引入了高速缓存(cache),比较新的,处理能力比较强的处理器,一般有三级高速缓存,分别为 L1 cache ,L2cache 以及 L3 cache。

- L1 cache 的访问速度与访问寄存器文件几乎一样快,容量大小为数万字节(KB 级别);

- L2 cache 的访问速度是 L1 cache 的五分之一,容量大小为数十万到数百万字节之间;

- L3 cache 的容量更大,同样访问速度与 L2 cache 相比也更慢

总线

- 地址总线

- 地址总线上能传送多少个不同的信息,CPU就可以对多少个存储单元寻址

- 一个CPU有N根地址线,即地址总线的宽度为N,最多可寻找2的N次方个内存单元

- 1个CPU的寻址能力为8KB,那么它的地址总线的宽度为13

- 数据总线

- 数据总线的宽度决定了CPU和外界的数据传送速度,8根数据总线一次可传送一个8位二进制数据(即一个字节),16根数据总线一次可传送两个字节

- 控制总线

- 有多少根控制总线,就意味着CPU提供了对外器件的多少种控制

一些约定/假定

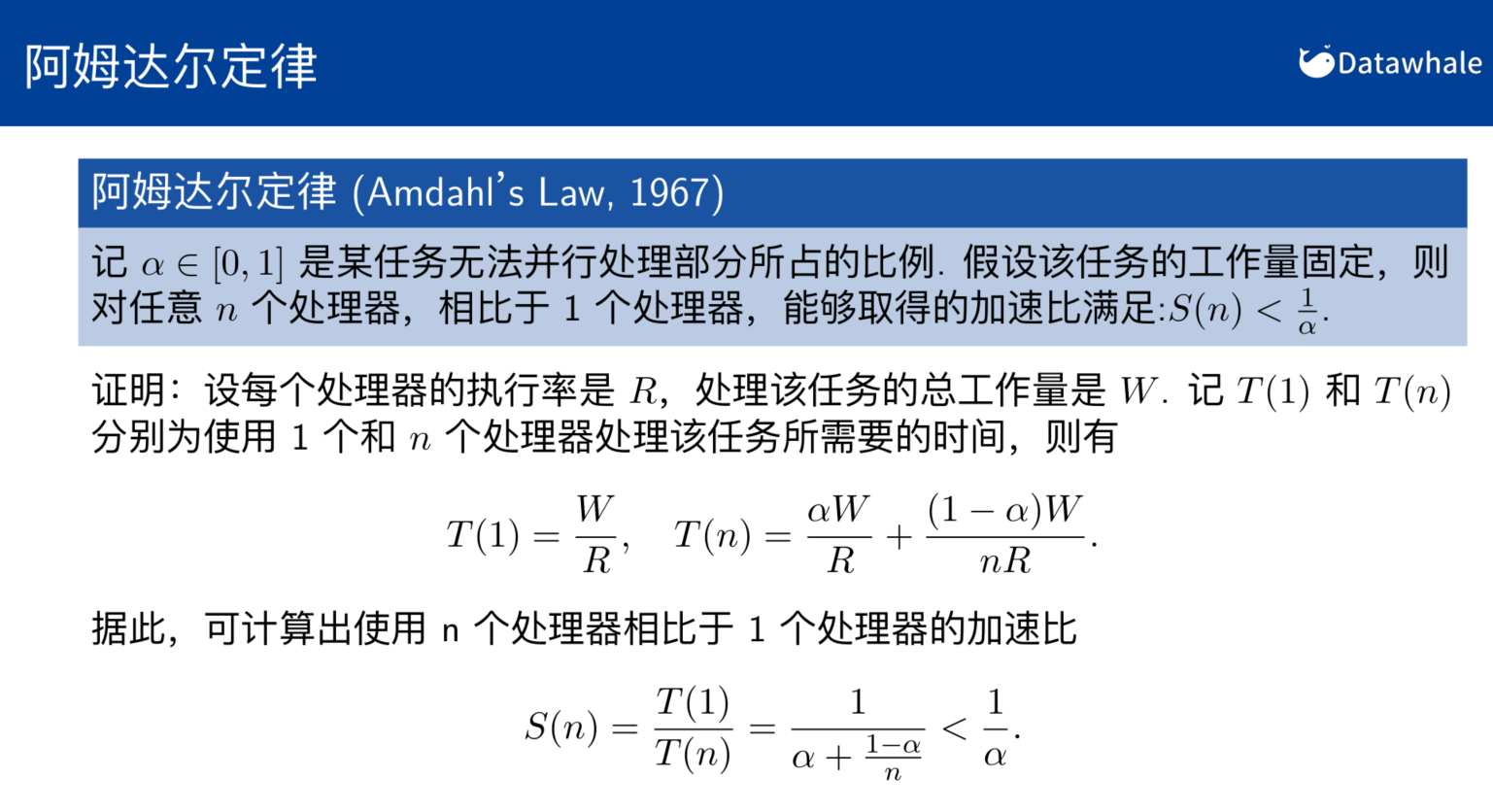

- 任务 (task):并行计算所处理的对象.

- 工作量 (workload):处理某任务的所需的各种开销的总和.

- 处理器 (processor):并行计算中所使用的最基本的处理器单元.

- 执行率 (execution rat):每个处理器单位时间能完成的工作量

- 执行时间 (execution time):处理某任务所需的时间.

- 加速比 (scalability):当处理器个数增多时,完成某固定工作量任务所需执行时间的减少数

- 理想加速比 (ideal scalability):处理器个数增多的比例.

- 并行效率 (parallel efficiency): 加速比 ÷ 理想加速比 ×100%

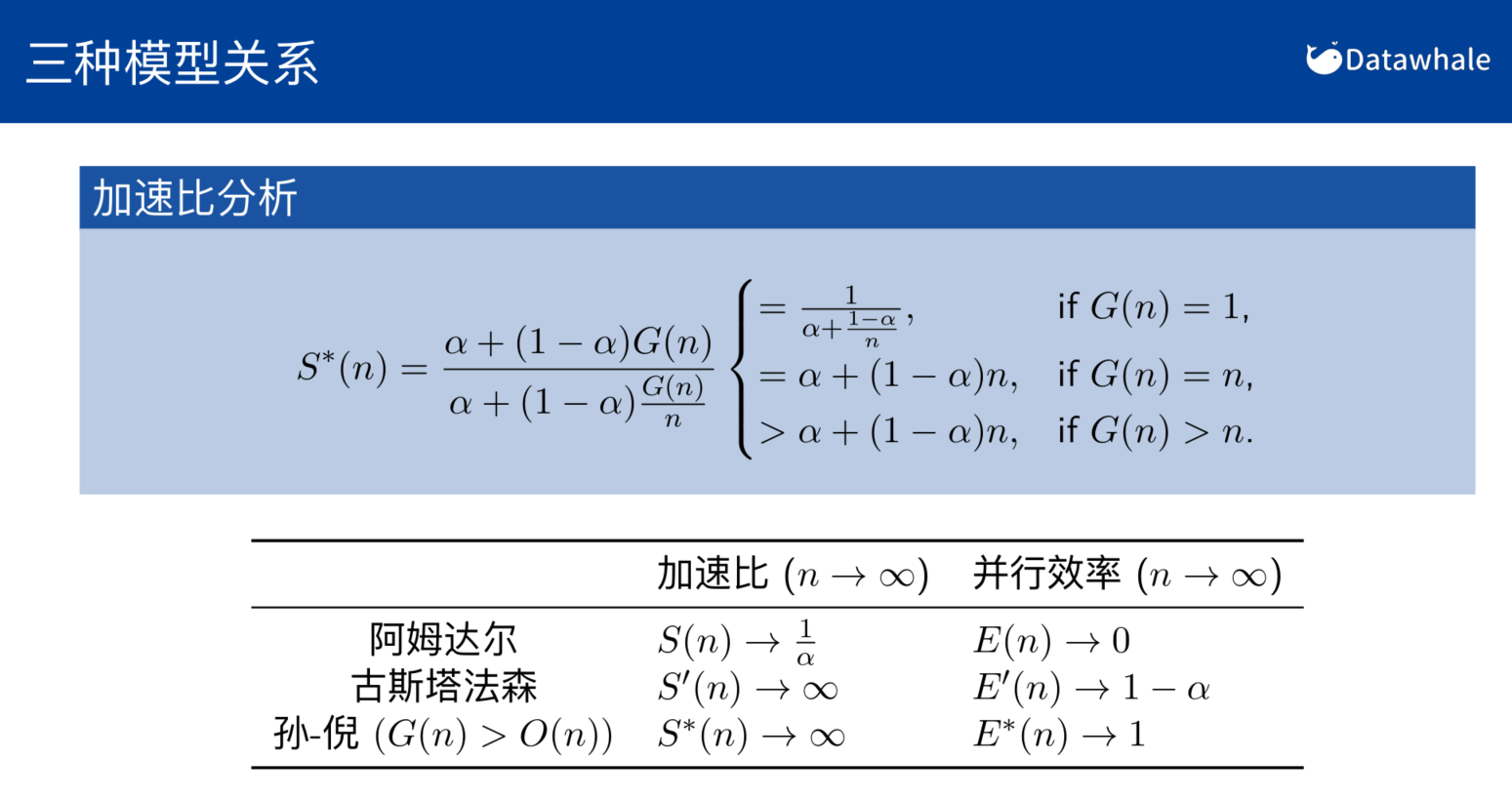

阿姆达尔定律

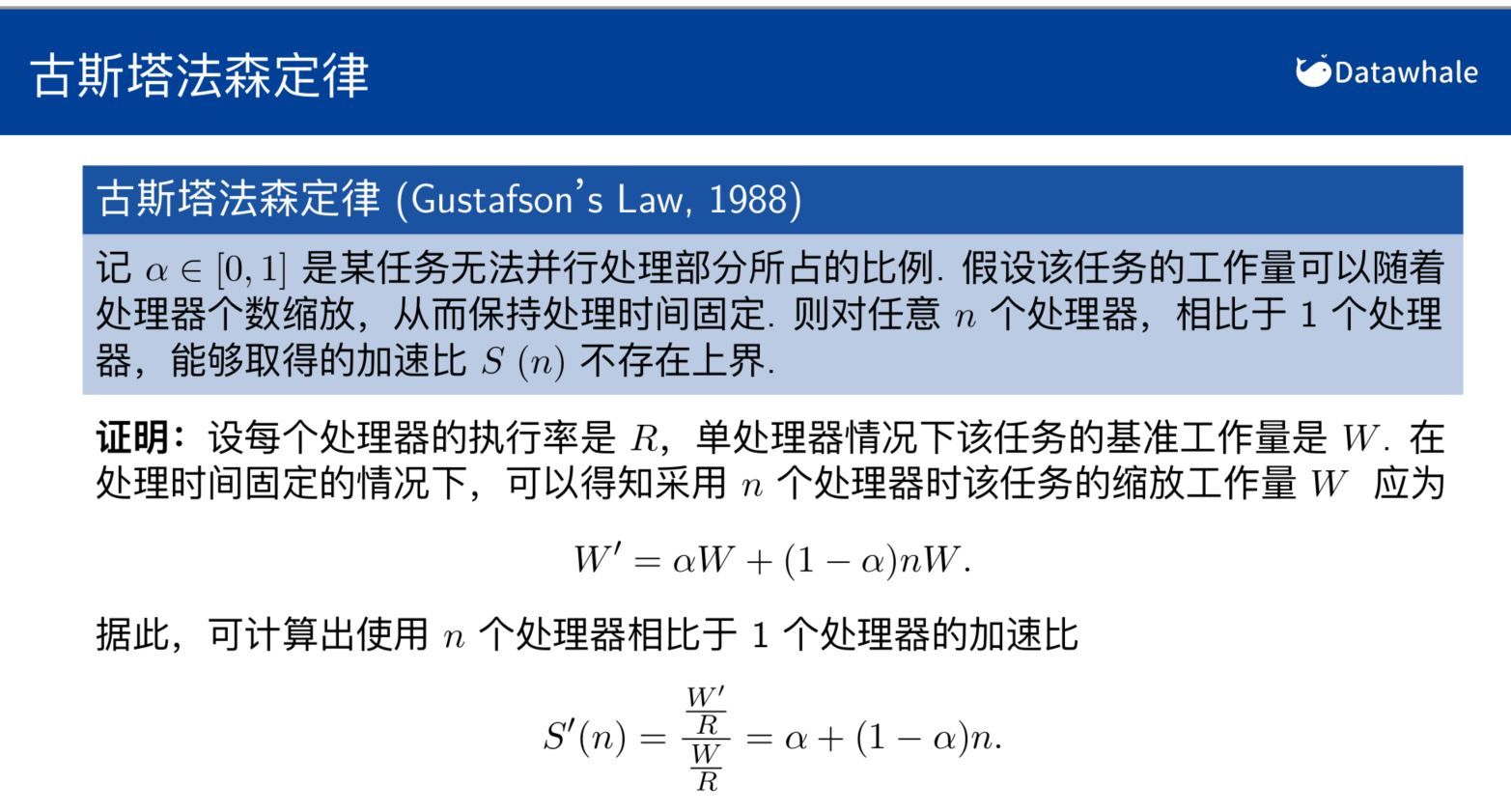

古斯塔法森定律

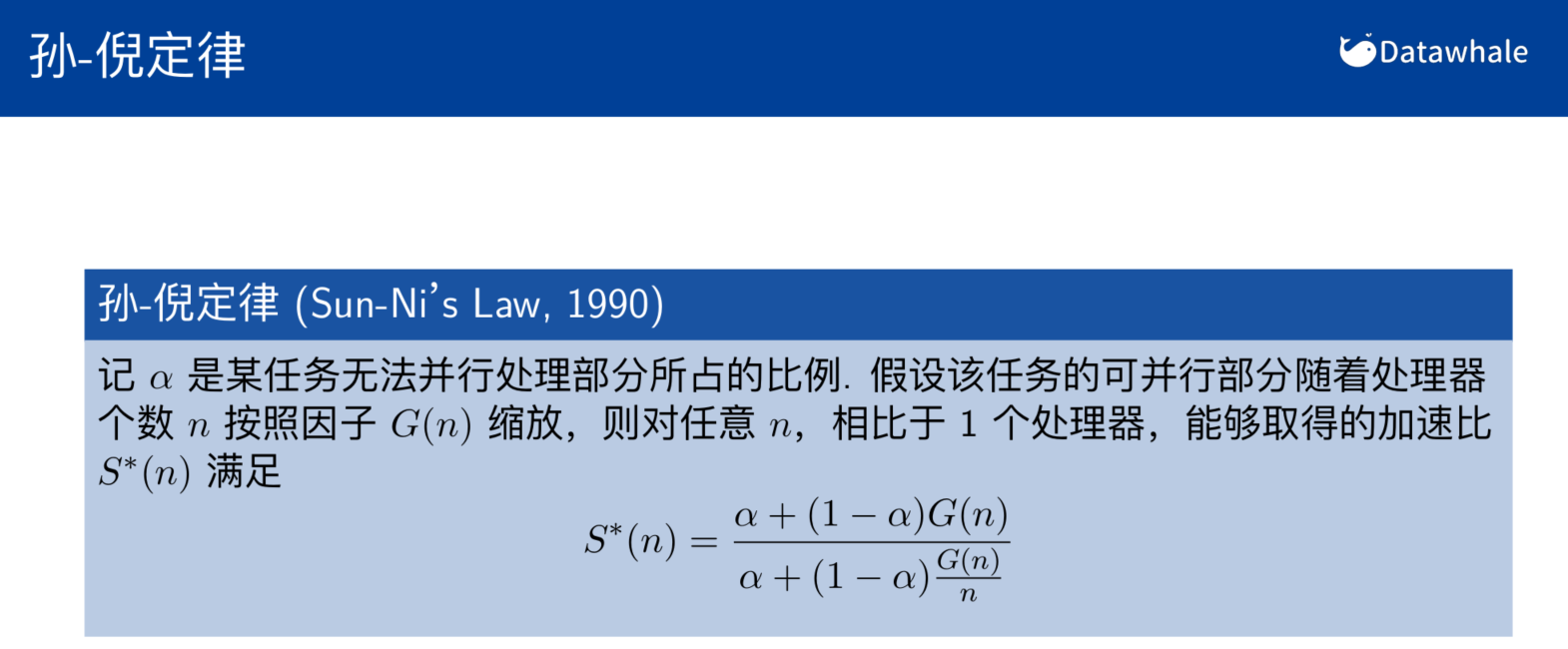

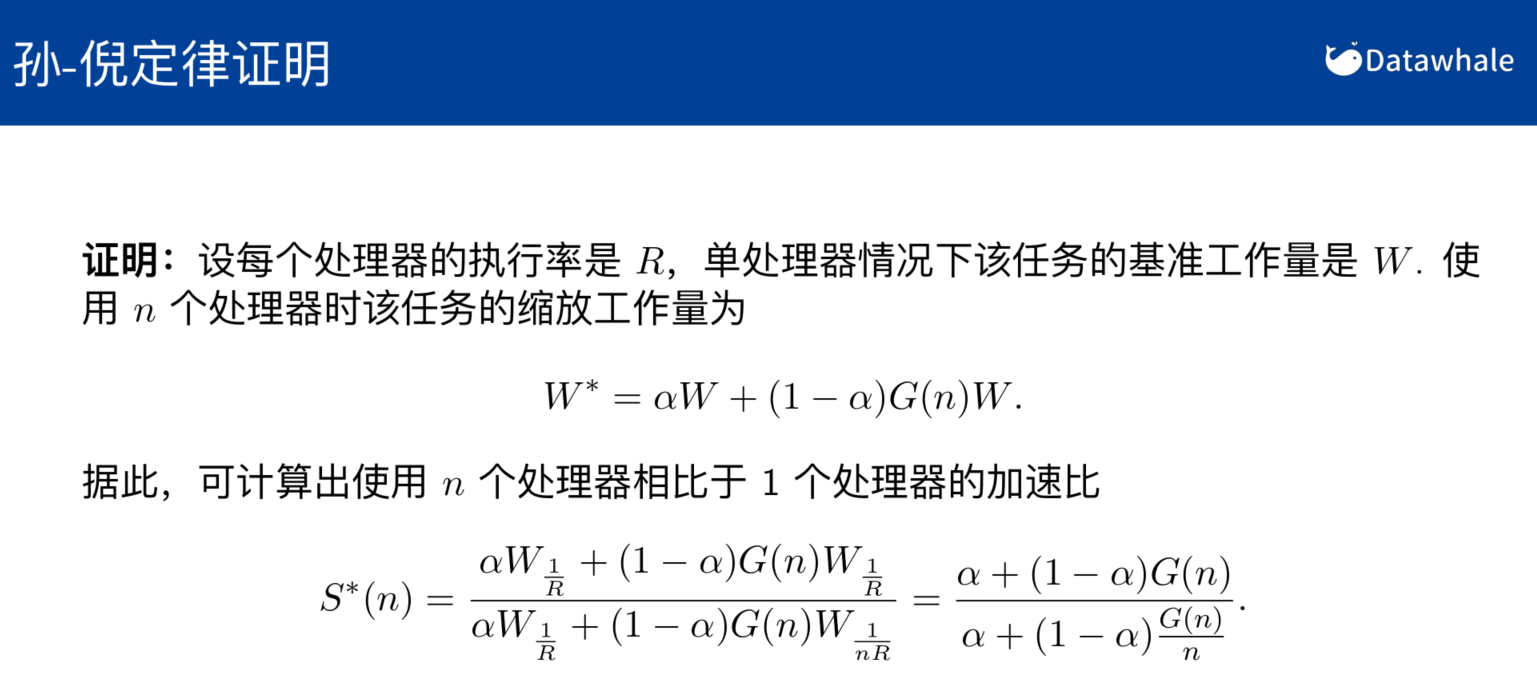

孙-倪定律

三种模型关系

拓展

- 在存储器中指令和数据没有任何区别,都是二进制信息

- 一个CPU可以引出3种总线的宽度标志不同方向的性能

- 地址总线的宽度决定了CPU的寻址能力

- 数据总线的宽度决定了CPU与其他器件进行数据传送时的一次数据传送量

- 控制总线的宽度决定了CPU对系统中其他器件的控制能力

参考资料

- Datawhale CSAPP组队学习

- 汇编语言_王爽_第四版

- 操作系统实战45讲